最先端LSI用SiベースMOSトランジスタに関する研究

カテゴリー

- 素材

- エレクトロニクス

SDGs

研究内容

Si LSIはこれまで過去40年以上に渡り、集積度が18ヶ月で2倍になるというMooreの法則に従ってチップあたりのトランジスタ数を増大させながら性能の向上を図ってきました。しかし、トランジスタのゲート長は20 nm以下になっており、半導体微細化は物理的限界に近づきつつあります。今後10-20年以内に半導体微細化が完全に終焉を迎え、LSIの性能向上が停滞してしまうと危惧されています。

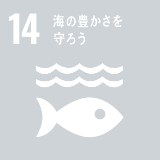

一方、Internet of Things(IoT)の進展と人工知能(AI)の台頭により、更なるコンピューティング能力の向上が必要とされています。このため、半導体微細化に依らずにLSIの性能向上を可能とする次世代コンピューティングに関する研究が世界中で活発化しています。当研究室では、AI・IoT時代を支える次世代半導体デバイスの研究を進めています。Si CMOSをベースとした技術開発およびSiプラットフォーム上にIII-V族半導体やGe、強誘電体材料を集積したトランジスタの研究をしています。

主な研究テーマ

-

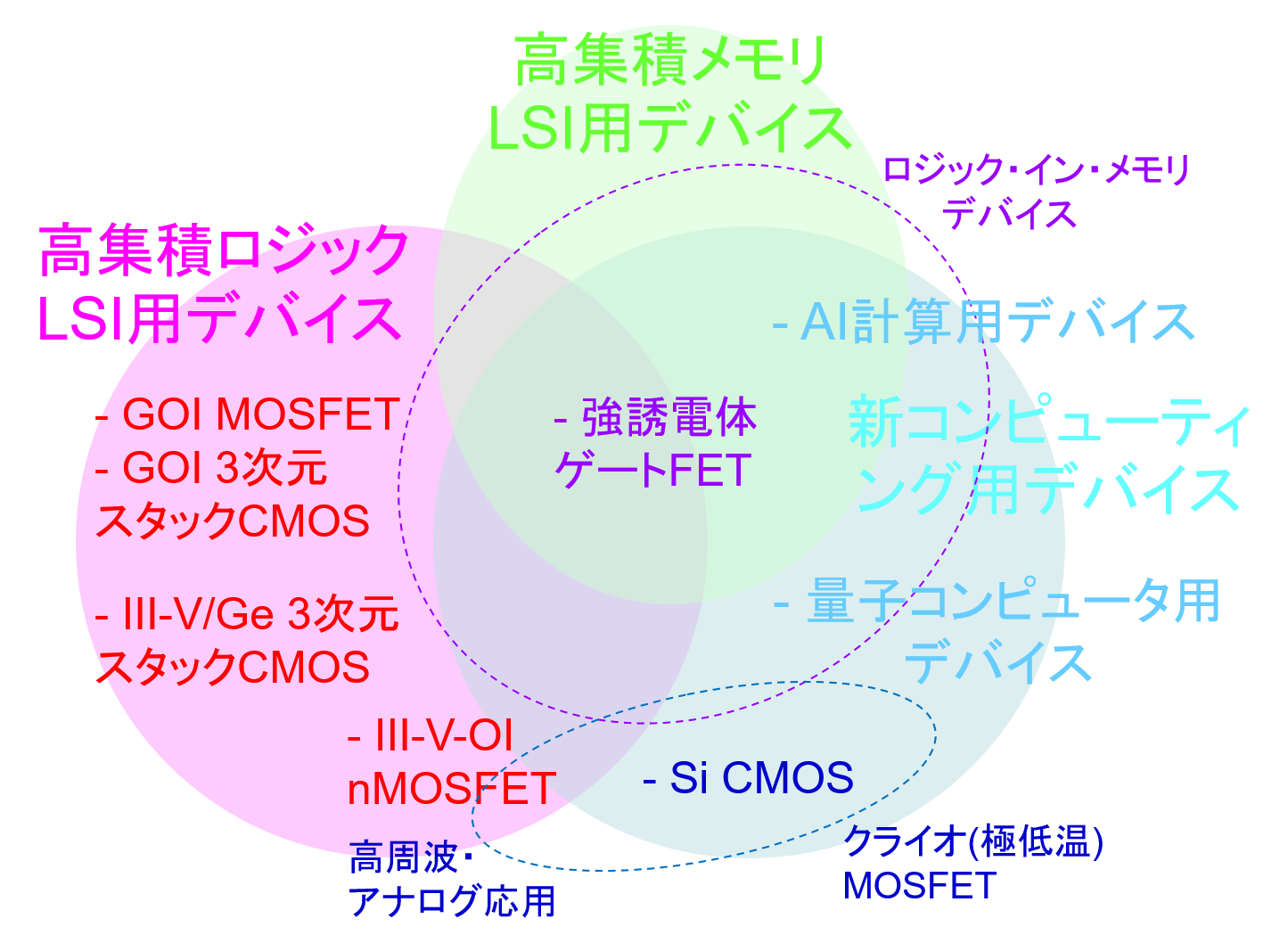

HfO2系強誘電体ゲート絶縁膜トランジスタと強誘電体メモリ

-

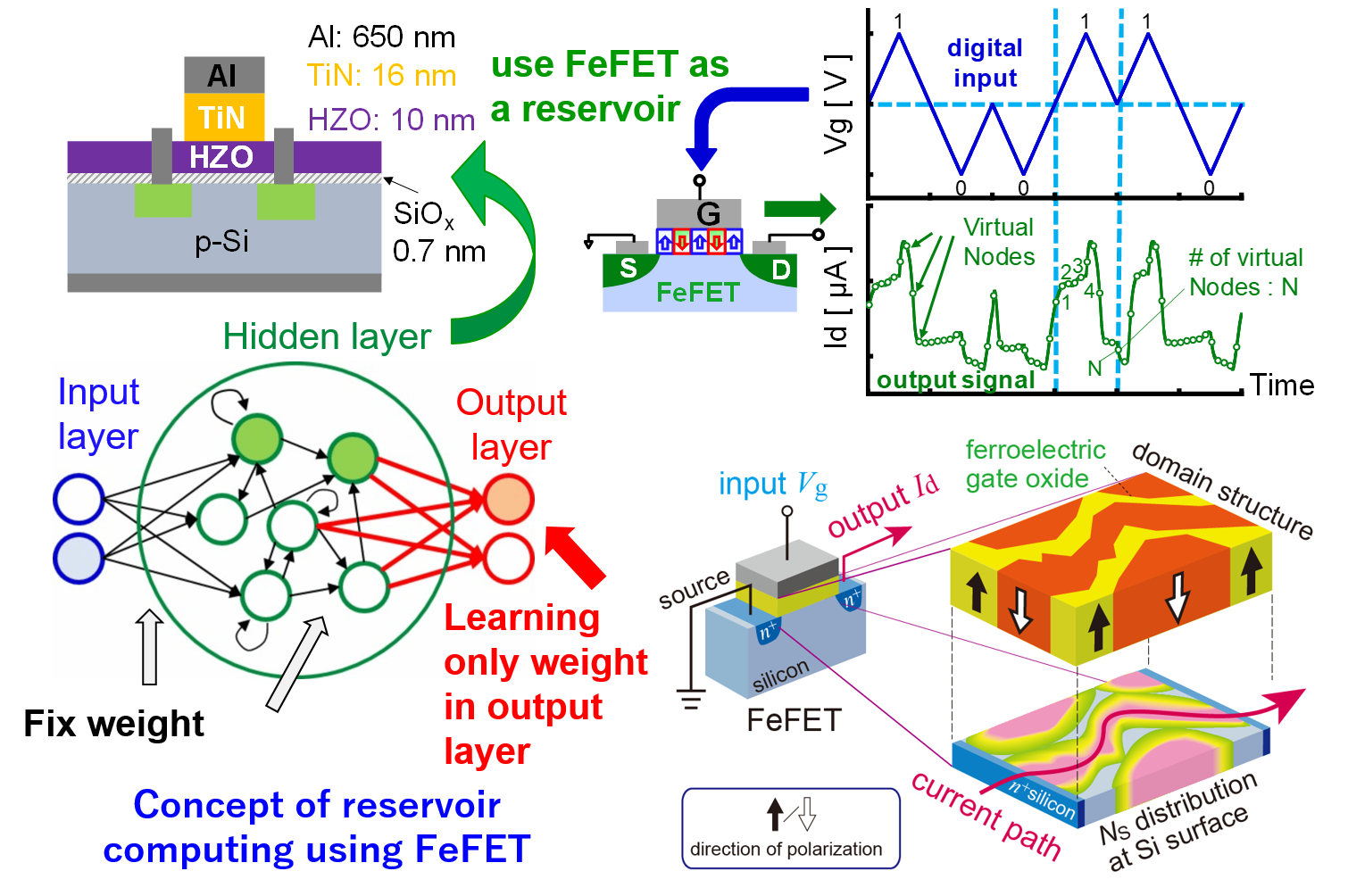

強誘電体デバイスを用いたリザバーコンピューティング

-

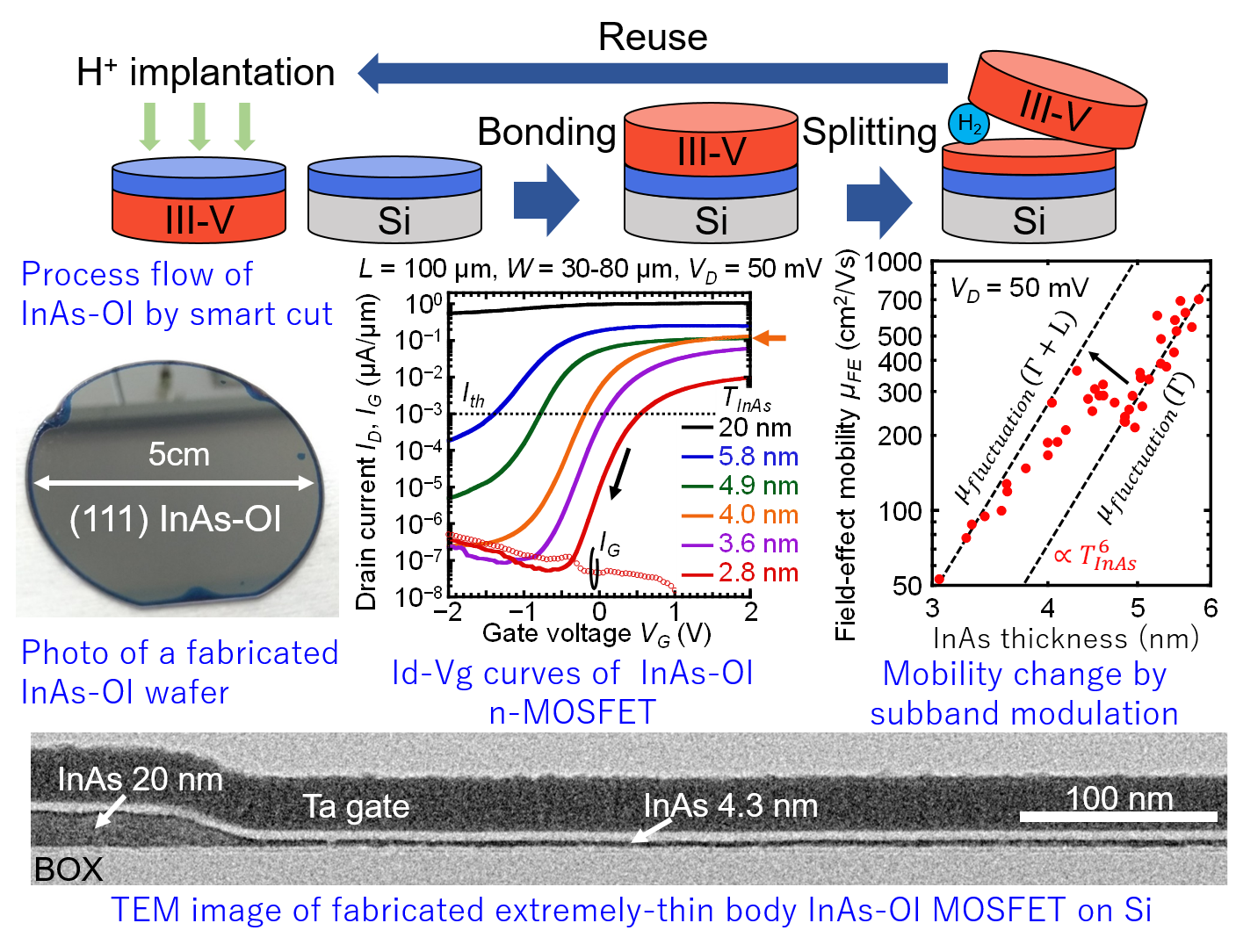

3次元集積CMOSのための極薄膜III-V-On-Insulator MOSFET

-

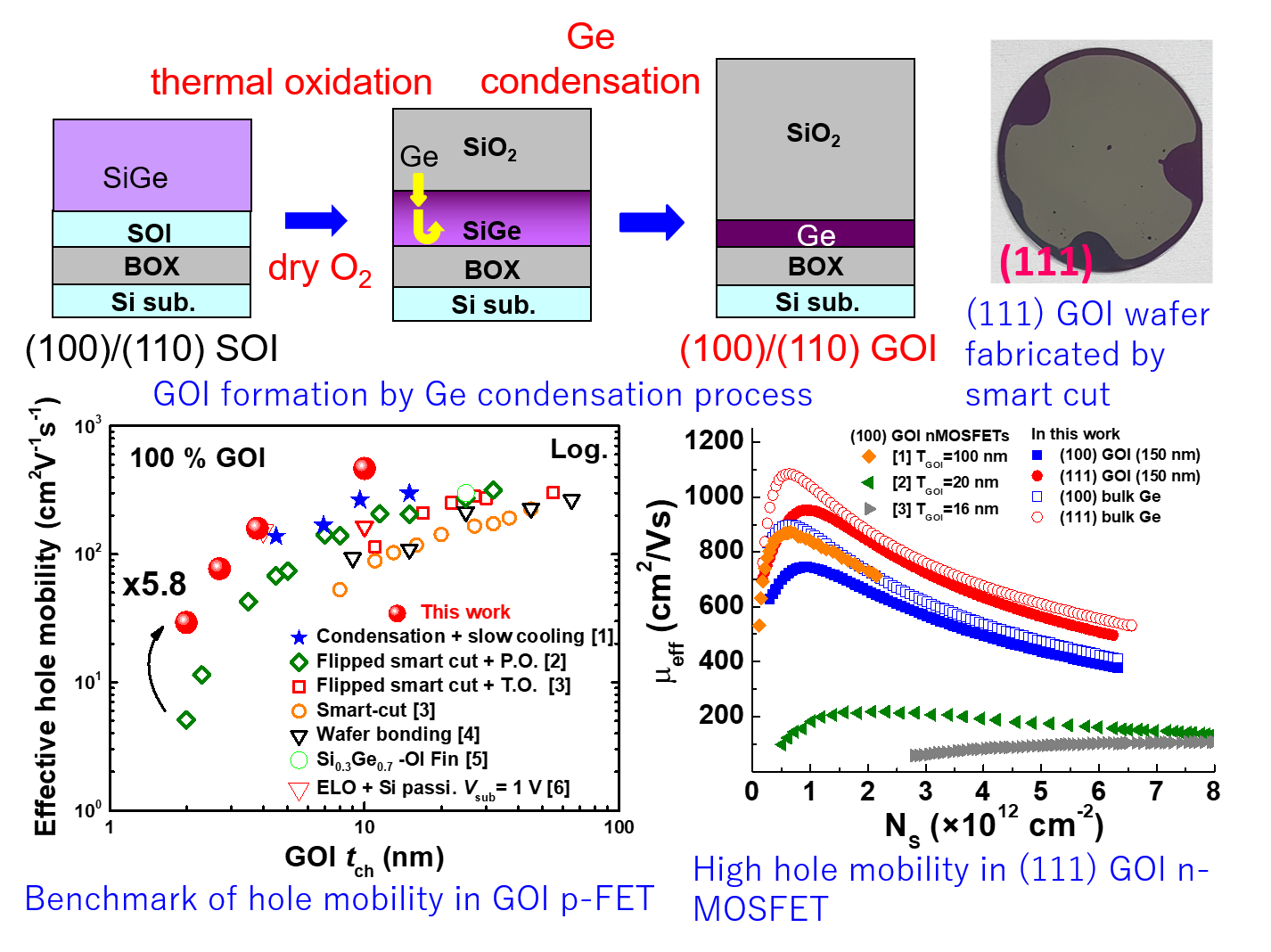

3次元集積CMOSのための極薄膜Ge-On-Insulator MOSFET

-

量子コンピュータのためのSi CMOSの極低温での動作特性の理解

これらに関し興味ある企業等との様々な情報交換の用意があります。

図1 研究対象としているデバイス

© 高木 信一

図2 HfZrO2ゲート絶縁膜を用いたFeFET

© 高木 信一

図3 FeFETを用いたリザバーコンピューティング

© 高木信一

図4 極薄膜InAs-On-Insulator MOSFETの作製と電気特性

© 高木信一

図5 極薄膜Ge-On-Insulator MOSFETの作製と電気特性

© 高木信一

想定される応用

AI・IoT時代を支えるSiプラットフォーム上の次世代半導体集積デバイスとこれらを用いた集積システム

連携への希望

これらに関し興味ある企業等との様々な情報交換の用意がある。

公開日 / 更新日

- 2021年12月01日

識別番号

- No. 00053-01